### Associative caching

2/3/25

## Administrivia

• HW 5 (linked lists in C) due Thursday night

- Midterm out Friday morning

- Multi-day takehome due sometime next week

- No class on Monday (2/10)

- Covers everything up to (and including) caching

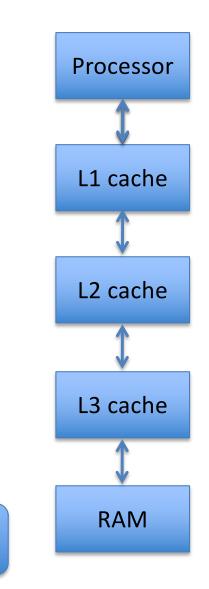

## Recall: Idea of caching

- Have small, fast memory near the processor and bigger, slower memory far way

- Locality:

tag

- temporal: Likely to reuse memory addresses soon

- spatial: Likely to use memory addresses near those we use now

line number

line in which this

address can be stored

offset

where addr falls

in cache line

Fully-associative caches: Any data block can use any line

Fully-associative caches: Any data block can use any line

What is the advantage of this?

How many bits would the tag occupy in a system with a 32-bit address space where the fully-associative cache stores 1024=2<sup>10</sup> lines, each holding 4 bytes?

- A. 18

- B. 20

- C. 26

- D. 30

- E. None of the above or cannot be determined

How many bits would the tag occupy in a system with a 32-bit address space where the fully-associative cache stores 1024=2<sup>10</sup> lines, each holding 4 bytes?

- A. 18

- B. 20

- C. 26

- D. <u>30</u>

- E. None of the above or cannot be determined

- Fully-associative caches: Any data block can use any line

- Replacement strategies: FIFO, LRU

- Fully-associative caches: Any data block can use any line

- Replacement strategies: FIFO, LRU

- Approximate LRU with just a couple of bits

- Fully-associative caches: Any data block can use any line

- Replacement strategies: FIFO, LRU

- Approximate LRU with just a couple of bits

- K-way set associative: Lines organized into sets, each data block can use any line in its set

How many bits would the tag occupy in a system with a 32-bit address space where the 4-way set associative cache stores 1024=2<sup>10</sup> lines, each holding 4 bytes?

- A. 18

- B. 20

- C. 22

- D. 24

- E. None of the above or cannot be determined

How many bits would the tag occupy in a system with a 32-bit address space where the 4-way set associative cache stores 1024=2<sup>10</sup> lines, each holding 4 bytes?

- A. 18

- B. 20

- C. <u>22</u>

- D. 24

- E. None of the above or cannot be determined

How many bits does the tag use in a system with a 32-bit address space where the 8-way set associative cache stores 2048=2<sup>11</sup> lines, each holding 16=2<sup>4</sup> bytes?

- A. 14

- B. 17

- C. 20

- D. 24

- E. None of the above or cannot be determined

How many bits does the tag use in a system with a 32-bit address space where the 8-way set associative cache stores 2048=2<sup>11</sup> lines, each holding 16=2<sup>4</sup> bytes?

- A. 14

- B. 17

- C. 20 (= 32 (11 3) 4)

D. 24

E. None of the above or cannot be determined

# What happens on a read to address 0011100?

#### (Cache is 2-way set associative, LRU, 2-byte lines)

|                |   | # | valid | tag  | data |

|----------------|---|---|-------|------|------|

| Set of 2 slots | 5 | 0 | Т     | 0011 | ???  |

|                | l | 1 | F     | 0010 | ???  |

|                | Ş | 2 | Т     | 1110 | ???  |

|                | ι | 3 | Т     | 1000 | ???  |

|                | ŗ | 4 | Т     | 1011 | ???  |

|                | ι | 5 | F     | 0011 | ???  |

|                | ۲ | 6 | Т     | 1011 | ???  |

| Hit            | ι | 7 | F     | 0010 | ???  |

A. Hit

B. Miss – loads line 3

C. Miss – loads line 4

D. Miss – loads line 5

E. None of the above or can't be determined

# What happens on a read to address 0011100?

#### (Cache is 2-way set associative, LRU, 2-byte lines)

|                |          | # | valid | tag  | data |

|----------------|----------|---|-------|------|------|

| Set of 2 slots | <u>ر</u> | 0 | Т     | 0011 | ???  |

|                | l        | 1 | F     | 0010 | ???  |

|                | Ş        | 2 | Т     | 1110 | ???  |

|                | l        | 3 | Т     | 1000 | ???  |

|                | ر<br>۲   | 4 | Т     | 1011 | ???  |

|                | l        | 5 | F     | 0011 | ???  |

|                | Ş        | 6 | Т     | 1011 | ???  |

| Hit            | l        | 7 | F     | 0010 | ???  |

A. Hit

B. Miss – loads line 3

C. Miss – loads line 4

- D. <u>Miss loads line 5</u>

- E. None of the above or can't be determined

# What happens on a read to address 0011011?

#### (Cache is 2-way set associative, LRU, 2-byte lines)

|                | #        | # valid    | tag  | data |

|----------------|----------|------------|------|------|

| Set of 2 lines | ſ        | т С        | 0011 | ???  |

|                | <b>۱</b> | <b>1</b> F | 0010 | ???  |

|                | ۽ ا      | <b>2</b> T | 1110 | ???  |

|                | l        | <b>3</b> T | 1000 | ???  |

|                | ے ک      | <b>4</b> T | 1011 | ???  |

|                | l        | 5 F        | 0011 | ???  |

|                | ۶ (      | 5 T        | 1011 | ???  |

| Hit            |          | <b>7</b> F | 0010 | ???  |

A. Hit

B. Miss – loads line 3

C. Miss – loads line 4

D. Miss – loads line 5

E. None of the above or can't be determined

# What happens on a read to address 0011011?

#### (Cache is 2-way set associative, LRU, 2-byte lines)

|                | 4        | # valid    | tag  | data |

|----------------|----------|------------|------|------|

| Set of 2 lines | ſ        | О Т        | 0011 | ???  |

|                | <b>۱</b> | 1 F        | 0010 | ???  |

|                | ; ۲      | <b>2</b> T | 1110 | ???  |

|                | l        | <b>3</b> T | 1000 | ???  |

|                | ۲ (      | <b>4</b> T | 1011 | ???  |

|                | ι        | 5 F        | 0011 | ???  |

|                | ر<br>ا   | 6 Т        | 1011 | ???  |

| Hit            | ι.       | <b>7</b> F | 0010 | ???  |

A. Hit

B. Miss – loads line 3

C. Miss – loads line 4

D. Miss – loads line 5

E. None of the above or <u>can't be determined (miss – loads 2 or 3)</u>

## What about writes?

Write-thru cache: Always send writes all the way down the memory hierarchy

- Write-back cache: Don't propagate changes down the hierarchy until data block is evicted

- Add "dirty bit" to each line

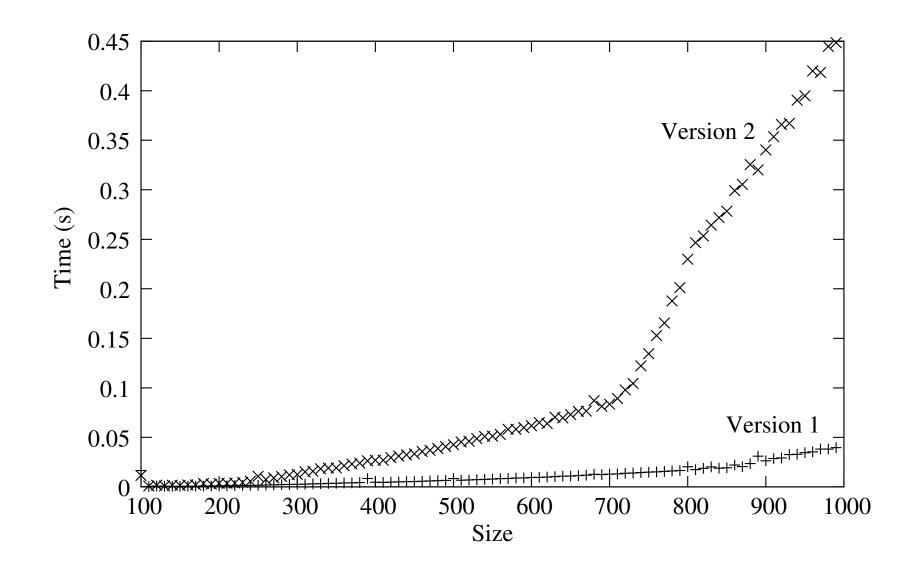

## Recall: Example of caching effects

```

Version 1: array[i][j] *= 2;

Version 2: array[j][i] *= 2;

```

Relevant detail: Java stores a 2D array as an array of array references

## Recall: Example of caching effects

```

int[][] array = new int[size][size];

for(int i=0; i < size; i++)

for(int j=0; j < size; j++)

/* DO SOMETHING */

Which version should have

better cache performance?

Version 1: array[i][i] *= 2;

A) Version 1

Version 2

B)

Version 2: array[j][i] *= 2;

```

Relevant detail: Java stores a 2D array as an array of array references

## Recall: Example of caching effects

```

int[][] array = new int[size][size];

for(int i=0; i < size; i++)

for(int j=0; j < size; j++)

/* DO SOMETHING */

Which version should have

better cache performance?

Version 1: array[i][j] *= 2;

Version 1

Version 2

B)

Version 2: array[j][i] *= 2;

```

Relevant detail: Java stores a 2D array as an array of array references